# DATABOUK Z8500 UNIVERSAL PERIPHERALS 1°T EDITION

BELL INDUSTRIES Electronics Distributor Division 1161 N. Fairoaks Avenue Sunnyvale, California 94086 (408) 734-8570 TWX NO. 910-339-9378

## Z8500 UNIVERSAL PERPHERALS ISSUED JANUARY 1983

## CONTENTS

|           | Page      |

|-----------|-----------|

| Z8530 SCC | 3 - 30    |

| Z8536 CIO | 31 - 64   |

| Z8538 FIO | 65 - 101  |

| Z8590 UPC | 103 - 129 |

## **Z8500** Universal Peripherals

SGS' Universal Peripheral Components Family is more than a group of simple I/O circuits—they are intelligent, fully programmable devices capable of performing complicated tasks independently. Their capabilities unburden the master CPU, reduce bus traffic, increase system throughput, and greatly simplify overall system hardware design requirements.

Z8500 series Universal Peripheral components are capable of interfacing with conventional non-multiplexed buses. All of them are extensively programmable to permit each to be tailored to its own applications. Also available is a series of functionally similar devices, identified by the number Z80xx, which interface with the Z-BUS<sup>TM</sup> or both the Z-BUS and conventional multiplexed buses.

Data communications problems are neatly handled by the Z8530 SCC Serial

**Communications Controller**. This device is a serial, dual-channel, multi-protocol controller which supports all popular communications formats. The SCC support virtually all serial data transfer applications.

Counting, timing, and parallel I/O transfer problems are easily solved using the **Z8536 CIO Counter/Timer and I/O Unit**. This components has three 16-bit counter/timers, three I/O ports, and can double as a programmable priority-interrupt controller.

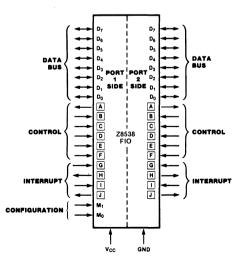

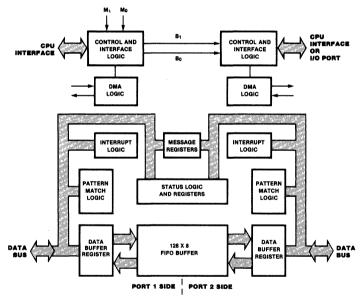

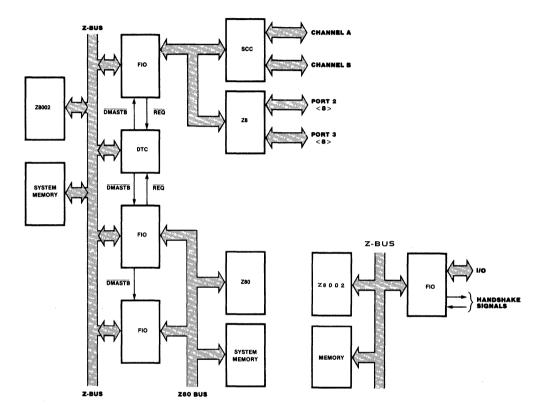

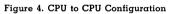

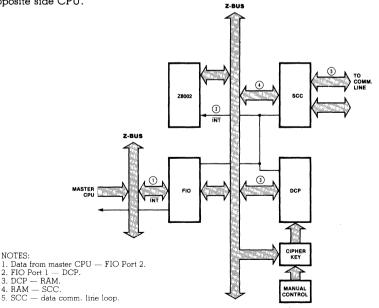

Interface problems with the interconnections of major components within an asynchronous, parallel processor system can be solved using the SCC **Z8538 FIO FIFO I/O Interface Unit**. This generalpurpose interface unit provides expandable, bidirectional buffering between asynchronous CPUs in a parallel processing network, or between a CPU and peripheral circuits and/or devices. The FIO can be used with system having either multiplexed or nonmultiplexed buses.

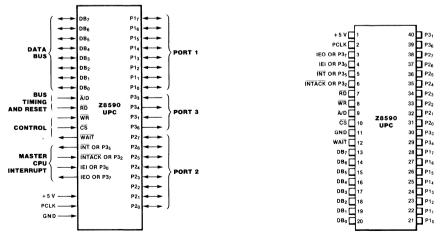

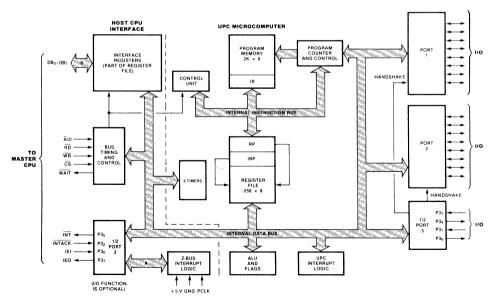

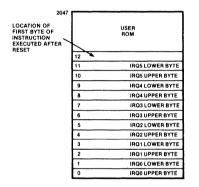

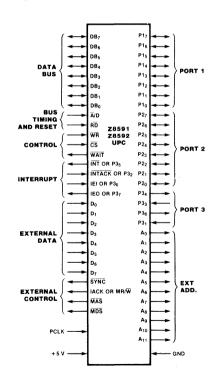

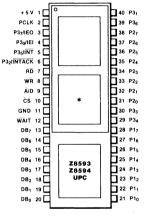

General-purpose control and data manipulation problems are easily handled by the **Z8590 UCP Universal Peripheral Controller**. The UPC is a complete microcomputer designed for offline applications. This microcomputer executes the same friendly capable instruction set as SGS' Z8<sup>TM</sup> microcomputer; it has three I/O ports, six levels of priority-interrupt, and 2K bytes of memory on chip. The UPC is intended for applications that require an intelligent peripheral controller which can assume many of the tasks normally required of the master CPU.

Ì

### Serial Communications Controller

#### Features

- Two independent, 0 to 1M bit/second, fullduplex channels, each with a separate crystal oscillator, baud rate generator, and Digital Phase-Locked Loop for clock recovery.

- Multi-protocol operation under program control; programmable for NRZ, NRZI, or FM data encoding.

- Asynchronous mode with five to eight bits and one, one and one-half, or two stop bits per character; programmable clock factor; break detection and generation; parity, overrun, and framing error detection.

- **General Description**

The Z8530 SCC Serial Communications Controller is a dual-channel, multi-protocol data communications peripheral designed for use with conventional non-multiplexed buses. The SCC functions as a serial-to-parallel, parallel-to-serial converter/controller. The SCC can be software-configured to satisfy a

- Synchronous mode with internal or external character synchronization on one or two synchronous characters and CRC generation and checking with CRC-16 or CRC-CCITT preset to either 1s or 0s.

- SDLC/HDLC mode with comprehensive frame-level control, automatic zero insertion and deletion, I-field residue handling, abort generation and detection, CRC generation and checking, and SDLC Loop mode operation.

- Local Loopback and Auto Echo modes.

wide variety of serial communications applications. The device contains a variety of new, sophisticated internal functions including on-chip baud rate generators, Digital Phase-Locked Loops, and crystal oscillators that dramatically reduce the need for external logic.

3

#### General Description (Continued)

The SCC handles asynchronous formats, Synchronous byte-oriented protocols such as IBM Bisync, and Synchronous bit-oriented protocols such as HDLC and IBM SDLC. This versatile device supports virtually any serial data transfer application (cassette, diskette, tape drives, etc.).

The device can generate and check CRC codes in any Synchronous mode and can be programmed to check data integrity in various modes. The SCC also has facilities for

#### **Pin Description**

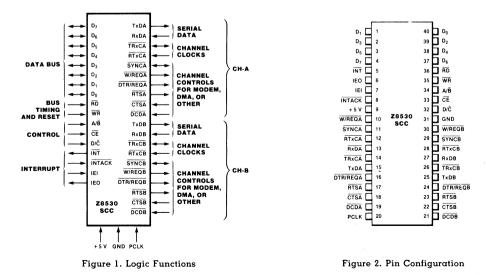

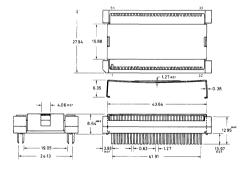

The following section describes the pin functions of the SCC. Figures 1 and 2 detail the respective pin functions and pin assignments.

$\mathbf{A}/\mathbf{B}$ . Channel A/Channel B Select (input). This signal selects the channel in which the read or write operation occurs.

**CE.** Chip Enable (input, active Low). This signal selects the SCC for a read or write operation.

**CTSA. CTSB.** Clear To Send (inputs, active Low). If these pins are programmed as Auto Enables, a Low on the inputs enables the respective transmitters. If not programmed as Auto Enables, they may be used as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow rise-time inputs. The SCC detects pulses on these inputs and can interrupt the CPU on both logic level transitions.

**D/C.** Data/Control Select (input). This signal defines the type of information transferred to or from the SCC. A High means data is transferred; a Low indicates a command.

**DCDA**, **DCDB**. Data Carrier Detect (inputs, active Low). These pins function as receiver enables if they are programmed for Auto Enables; otherwise they may be used as general-purpose input pins. Both pins are Schmitt-trigger buffered to accomodate slow rise-time signals. The SCC detects pulses on

modem controls in both channels. In applications where these controls are not needed, the modem controls can be used for general-purpose I/O.

The Z-BUS daisy-chain interrupt hierarchy is also supported — as is standard for SGS peripheral components.

The Z8530 SCC is packaged in a 40-pin ceramic DIP and uses a single +5 V power supply.

these pins and can interrupt the CPU on both logic level transitions.

**D**<sub>0</sub>-**D**<sub>7</sub>. Data Bus (bidirectional, 3-state). These lines carry data and commands to and from the SCC.

**DTR/REQA**, **DTR/REQB**. Data Terminal Ready/Request (outputs, active Low). These outputs follow the state programmed into the DTR bit. They can also be used as generalpurpose outputs or as Request lines for a DMA controller.

**IEI.** Interrupt Enable In (input, active High). IEI is used with IEO to form an interrupt daisy chain when there is more than one interruptdriven device. A High IEI indicates that no other higher priority device has an interrupt under service or is requesting an interrupt.

**IEO.** Interrupt Enable Out (output, active High). IEO is High only if IEI is High and the CPU is not servicing an SCC interrupt or the SCC is not requesting an interrupt (Interrupt Acknowledge cycle only). IEO is connected to the next lower priority device's IEI input and thus inhibits interrupts from lower priority devices.

**INT.** Interrupt Request (output, open-drain, active Low). This signal is activated when the SCC requests an interrupt.

**INTACK.** Interrupt Acknowledge (input, active Low). This signal indicates an active Interrupt Acknowledge cycle. During this cycle, the

#### Pin Description (Continued)

SCC interrupt daisy chain settles. When RD becomes active, the SCC places an interrupt <u>vector on</u> the data bus (if IEI is High). <u>INTACK</u> is latched by the rising edge of PCLK.

**PCLK.** *Clock* (input). This is the master SCC clock used to synchronize internal signals PCLK is a TTL level signal.

**RD.** *Read* (input, active Low). This signal indicates a read operation and when the SCC is selected, enables the SCC's bus drivers. During the Interrupt Acknowledge cycle, this signal gates the interrupt vector onto the bus if the SCC is the highest priority device requesting an interrupt.

**RxDA, RxDB.** *Receive Data* (inputs, active High). These input signals receive serial data at standard TTL levels.

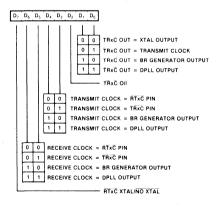

**RTxCA**, **RTxCB**. Receive/Transmit Clocks (inputs, active Low). These pins can be programmed in several different modes of operation. In each channel,  $\overline{\text{RTxC}}$  may supply the receive clock, the transmit clock, the clock for the baud rate generator, or the clock for the Digital Phase-Locked Loop. These pins can also <u>be programmed</u> for use with the respective SYNC pins as a crystal oscillator. The receive clock may be 1, 16, 32, or 64 times the data rate in Asynchronous modes.

**RTSA**, **RTSB**. Request To Send (outputs, active Low). When the Request To Send (RTS) bit in Write Register 5 (Figure 11) is set, the RTS signal goes Low. When the RTS bit is reset in the Asynchronous mode and Auto Enable is on, the signal goes High after the transmitter is empty. In Synchronous mode or in Asynchronous mode with Auto Enable off, the RTS pin strictly follows the state of the RTS bit. Both pins can be used as general-purpose outputs.

**SYNCA. SYNCB.** Synchronization (inputs or outputs, active Low). These pins can act either as inputs, outputs, or part of the crystal oscillator circuit. In the Asynchronous Receive mode (crystal oscillator option not selected), these pins are inputs similar to CTS and DCD. In this mode, transitions on these lines affect

the state of the Synchronous/Hunt status bits in Read Register 0 (Figure 10) but have no other function.

78530 SCC

In External Synchronization mode with the crystal oscillator not selected, these lines also act as inputs. In this mode,  $\overline{\text{SYNC}}$  must be driven Low two receive clock cycles after the last bit in the synchronous character is received. Character assembly begins on the rising edge of the receive clock immediately preceding the activation of  $\overline{\text{SYNC}}$ .

In the Internal Synchronization mode (Monosync and Bisync) with the crystal oscillator not selected, these pins act as outputs and are active only during the part of the receive clock cycle in which synchronous characters are recognized. The synchronous condition is not latched, so these outputs are active each time a synchronization pattern is recognized (regardless of character boundaries). In SDLC mode, these pins act as outputs and are valid on receipt of a flag.

**TxDB.** *TxDB. Transmit Data* (outputs, active High). These output signals transmit serial data at standard TTL levels.

**TRxCA**, **TRxCB**. Transmit/Receive Clocks (inputs or outputs, active Low). These pins can be programmed in several different modes of operation. TRxC may supply the receive clock or the transmit clock in the input mode or supply the output of the Digital Phase-Locked Loop, the crystal oscillator, the baud rate generator, or the transmit clock in the output mode.

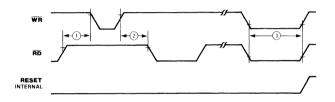

**WR.** Write (input, active Low). When the SCC is selected, this signal indicates a write operation. The coincidence of  $\overline{RD}$  and  $\overline{WR}$  is interpreted as a reset.

**W/REQA, W/REQB.** Wait/Request (outputs, open-drain when programmed for a Wait function, driven High or Low when programmed for a Request function). These dual-purpose outputs may be programmed as Request lines for a DMA controller or as Wait lines to synchronize the CPU to the SCC data rate. The reset state is Wait.

#### **Functional Description**

The functional capabilities of the SCC can be described from two different points of view: as a data communications device, it transmits and receives data in a wide variety of data communications protocols; as a microprocessor peripheral, the SCC offers valuable features such as vectored interrupts, polling, and simple handshake capability.

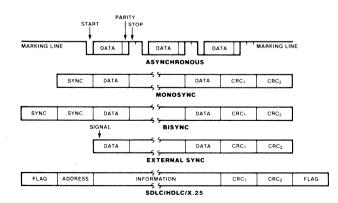

**Data Communications Capabilities.** The SCC provides two independent full-duplex channels programmable for use in any common Asynchronous or Synchronous data-communication protocol. Figure 3 and the following description briefly detail these protocols.

Asynchronous Modes. Transmission and reception can be accomplished independently on each channel with five to eight bits per character, plus optional even or odd parity. The transmitters can supply one, one-and-ahalf, or two stop bits per character and can provide a break output at any time. The receiver break-detection logic interrupts the CPU both at the start and at the end of a received break. Reception is protected from spikes by a transient spike-rejection mechanism that checks the signal one-half a bit time after a Low level is detected on the receive data input (RxDA or RxDB in Figure 1). If the Low does not persist (as in the case of a transient), the character assembly process does not start.

Framing errors and overrun errors are detected and buffered together with the partial character on which they occur. Vectored interrupts allow fast servicing or error conditions using dedicated routines. Furthermore, a built-in checking process avoids the interpretation of a framing error as a new start bit: a framing error results in the addition of one-half a bit time to the point at which the search for the next start bit begins.

The SCC does not require symmetric transmit and receive clock signals—a feature allowing use of the wide variety of clock sources. The transmitter and receiver can handle data at a rate of 1, 1/16, 1/32, or 1/64 of the clock rate supplied to the receive and transmit clock inputs. In Asynchronous modes, the SYNC pin may be programmed as an input used for functions such as monitoring a ring indicator.

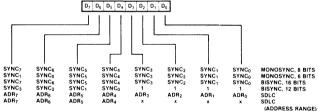

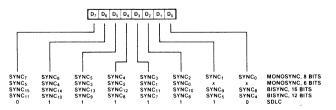

Synchronous Modes. The SCC supports both byte-oriented and bit-oriented synchronous communication. Synchronous byte-oriented protocols can be handled in several modes,

## **STS** 28530 SCC

#### Functional Description (Continued)

allowing character synchronization with a 6-bit or 8-bit synchronous character (Monosync), any 12-bit synchronization pattern (Bisync), or with an external synchronous signal. Leading sync characters can be removed without interrupting the CPU.

Five- or 7-bit synchronous characters are detected with 8- or 16-bit patterns in the SCC by overlapping the larger pattern across multiple incoming synchronous characters as shown in Figure 4.

CRC checking for Synchronous byteoriented modes is delayed by one character time so that the CPU may disable CRC checking on specific characters. This permits the implementation of protocols such as IBM Bisync.

Both CRC-16 (X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1) and CCITT  $(X^{16} + X^{12} + X^5 + 1)$  error checking polynomials are supported. Either polynomial may be selected in all Synchronous modes. Users may preset the CRC generator and checker to all 1s or all 0s. The SCC also provides a feature that automatically transmits CRC data when no other data is available for transmission. This allows for high speed transmissions under DMA control, with no need for CPU intervention at the end of a message. When there is no data or CRC to send in Synchronous modes, the transmitter inserts 6-, 8-, or 16-bit synchronous characters, regardless of the programmed character length.

The SCC supports Synchronous bit-oriented protocols, such as SDLC and HDLC, by performing automatic flag sending, zero insertion, and CRC generation. A special command can be used to abort a frame in transmission. At the end of a message, the SCC automatically transmits the CRC and trailing flag when the transmitter underruns. The transmitter may also be programmed to send an idle line consisting of continuous flag characters or a steady marking condition.

If a transmit underrun occurs in the middle of a message, an external/status interrupt warns the CPU of this status change so that an abort may be issued. The SCC may also be programmed to send an abort itself in case of an underrun, relieving the CPU of this task. One to eight bits per character can be sent, allowing reception of a message with no prior information about the character structure in the information field of a frame.

The receiver automatically acquires synchronization on the leading flag of a frame in SDLC or HDLC and provides a synchronization signal on the SYNC pin (an interrupt can also be programmed). The receiver can be programmed to search for frames addressed by a single byte (or four bits within a byte) of a user-selected address or to a global broadcast address. In this mode, frames not matching either the user-selected or broadcast address are ignored. The number of address bytes can be extended under software control. For receiving data, an interrupt on the first received character, or an interrupt on every character, or on special condition only (endof-frame) can be selected. The receiver automatically deletes all 0s inserted by the transmitter during character assembly. CRC is also calculated and is automatically checked to validate frame transmission. At the end of transmission, the status of a received frame is available in the status registers. In SDLC mode, the SCC must be programmed to use the SDLC CRC polynomial, but the generator and checker may be preset to all 1s or all 0s. The CRC is inverted before transmission and the receiver checks against the bit pattern 0001110100001111.

#### Figure 4. Detecting 5 - or 7 - Bit Synchronous Characters

7

NRZ, NRZI or FM coding may be used in any lx mode. The parity options available in Asynchronous modes are available in Synchronous modes.

The SCC can be conveniently used under DMA control to provide high speed reception or transmission. In reception, for example, the SCC can interrupt the CPU when the first character of a message is received. The CPU then enables the DMA to transfer the message to memory. The SCC then issues an end-offrame interrupt and the CPU can check the status of the received message. Thus, the CPU is freed for other service while the message is being received. The CPU may also enable the DMA first and have the SCC interrupt only on end-of-frame. This procedure allows all data to be transferred via the DMA.

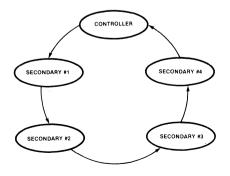

**SDLC Loop Mode.** The SCC supports SDLC Loop mode in addition to normal SDLC. In an SDLC Loop, there is a primary controller station that manages the message traffic flow on the loop and any number of secondary stations. In SDLC Loop mode, the SCC performs the functions of a secondary station while an SCC operating in regular SDLC mode can act as a controller (Figure 5).

A secondary station in an SDLC Loop is always listening to the messages being sent around the loop, and in fact must pass these messages to the rest of the loop by retransmitting them with a one-bit-time delay. The secondary station can place its own message

Figure 5. An SDLC Loop

on the loop only at specific times. The controller signals that secondary stations may transmit messages by sending a special character, called an EOP (End Of Poll), around the loop. The EOP character is the bit pattern 1111110. Because of zero insertion during messages, this bit pattern is unique and easily recognized.

When a secondary station has a message to transmit and recognizes an EOP on the line, it changes the last binary 1 of the EOP to a 0 before transmission. This has the effect of turning the EOP into a flag sequence. The secondary station now places its message on the loop and terminates the message with an EOP. Any secondary stations further down the loop with messages to transmit can then append their messages to the message of the first secondary station by the same process. Any secondary stations without messages to send merely echo the incoming messages and are prohibited from placing messages on the loop (except upon recognizing an EOP).

SDLC Loop mode is a programmable option in the SCC. NRZ, NRZI, and FM coding may all be used in SDLC Loop mode.

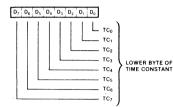

Baud Rate Generator. Each channel in the SCC contains a programmable baud rate generator. Each generator consists of two 8-bit time constant registers that form a 16-bit time constant, a 16-bit down counter, and a flip-flop on the output producing a square wave. On startup, the flip-flop on the output is set in a High state, the value in the time constant register is loaded into the counter, and the counter starts counting down. The output of the baud rate generator toggles upon reaching 0, the value in the time constant register is loaded into the counter, and the process is repeated. The time constant may be changed at any time, but the new value does not take effect until the next load of the counter.

The output of the baud rate generator may be used as either the transmit clock, the receive clock, or both. It can also drive the Digital Phase-Locked Loop (see next section).

If the receive clock or transmit clock is not programmed to come from the TRxC pin, the

output of the baud <u>rate</u> generator may be echoed out via the <u>TRxC</u> pin.

The following formula relates the time constant to the baud rate (the baud rate is in bits/second and the BR clock period is in seconds):

| baud rate |   | 1                                                |

|-----------|---|--------------------------------------------------|

| Daug rate | = | 2 (time constant + 2) $\times$ (BR clock period) |

**Digital Phase-Locked Loop.** The SCC contains a Digital Phase-Locked-Loop (DPLL) to recover clock information from a data stream with NRZI or FM encoding. The DPLL is driven by a clock that is nominally 32 (NRZI) or 16 (FM) times the data rate. The DPLL uses this clock, along with the data stream, to construct a clock for the data. This clock may then be used as the SCC recive clock, the transmit clock, or both.

For NRZI encoding, the DPLL counts the 32x clock to create nominal bit times. As the 32x clock is counted, the DPLL is searching the incoming data stream for edges (either 1 to 0 or 0 to 1). Whenever an edge is detected, the DPLL makes a count adjustment (during the next counting cycle), producing a terminal count closer to the center of the bit cell.

For FM encoding, the DPLL still counts from 0 to 31, but with a cycle corresponding to two bit times. When the DPLL is locked, the clock edges in the data stream should occur between counts 15 and 16 and between counts 31 and 0. The DPLL looks for edges only during a time centered on the 15 to 16 counting transition.

The 32x clock for the DPLL can be programmed to come from either the  $\overline{RTxC}$  input or the output of the baud rate generator. The DPLL output may be programmed to be echoed out of the SCC via the  $\overline{TRxC}$  pin (if this pin is not being used as an input).

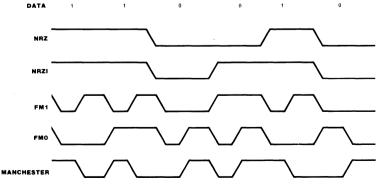

Data Encoding. The SCC may be programmed to encode and decode the serial data in four different ways (Figure 6). In NRZ encoding, a 1 is represented by a High level and a 0 is represented by a Low level. In NRZI encoding, a l is represented by no change in level and a 0 is represented by a change in level. In FM1 (more properly, bi-phase mark). a transition occurs at the beginning of every bit cell. A 1 is represented by an additional transition at the center of the bit cell and a 0 is represented by no additional transition at the center of the bit cell. In FMO (bi-phase space), a transition occurs at the beginning of every bit cell. A 0 is represented by an additional transition at the center of the bit cell, and a 1 is represented by no additional transition at the center of the bit cell. In addition to these four methods, the SCC can be used to decode

Figure 6. Data Encoding Methods

Manchester (bi-phase level) data by using the DPLL in the FM mode and programming the receiver for NRZ data. Manchester encoding always produces a transition at the center of the bit cell. If the transition is 0 to 1, the bit is a 0. If the transition is 1 to 0, the bit is a 1.

Auto Echo and Local Loopback. The SCC is capable of automatically echoing everything it receives. This feature is useful mainly in Asynchronous modes, but works in Synchronous and SDLC modes as well. In Auto Echo mode, TxD is RxD. Auto Echo mode can be used with NRZI or FM encoding with no additional delay, because the data stream is not decoded before retransmission. In Auto Echo mode, the  $\overline{\text{CTS}}$  input is ignored as a transmitter enable (although transitions on this input can still cause interrupts if programmed to do so). In this mode, the transmitter is actually bypassed and the programmer is responsible for disabling transmitter interrupts and WAIT/REQUEST on transmit.

The SCC is also capable of local loopback. In this mode TxD is RxD, just as in Auto Echo mode. However, in Local Loopback mode, the internal transmit data is tied to the internal receive data and RxD is ignored (except to be echoed out via TxD). The CTS and DCD inputs are also ignored as transmit and receive enables. However, transitions on these inputs can still cause interrupts. Local Loopback works in Asynchronous, Synchronous and SDLC modes with NRZ, NRZI or FM coding of the data stream.

**I/O Interface Capabilities.** The SCC offers the choice of Polling, Interrupt (vectored or nonvectored), and Block Transfer modes to transfer data, status, and control information to and from the CPU. The Block Transfer mode can be implemented under CPU or DMA control.

**Polling.** All interrupts are disabled. Three status registers in the SCC are automatically updated whenever any function is performed. For example, end-of-frame in SDLC mode sets a bit in one of these status registers. The idea behind polling is for the CPU to periodically read a status register until the

register contents indicate the need for data to be transferred. Only one register needs to be read; depending on its contents, the CPU either writes data, reads data, or continues. Two bits in the register indicate the need for data transfer. An alternative is a poll of the Interrupt Pending register to determine the source of an interrupt. The status for both channels resides in one register.

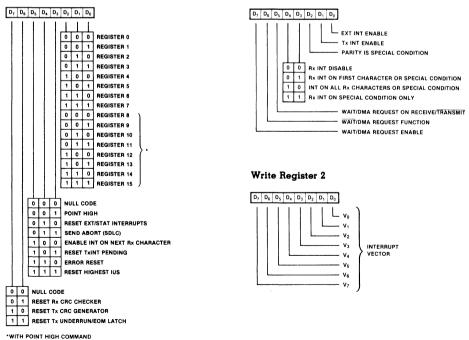

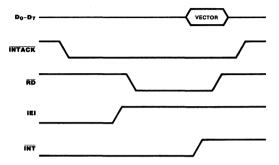

**Interrupts.** When an SCC responds to an Interrupt Acknowledge signal (INTACK) from the CPU, an interrupt vector may be placed on the data bus. This vector is written in WR2 and may be read in RR2A or RR2B (Figures 10 and 11).

To speed interrupt response time, the SCC can modify three bits in this vector to indicate status. If the vector is read in Channel A, status is never included; if it is read in Channel B, status is always included.

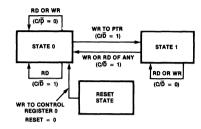

Each of the six sources of interrupts in the SCC (Transmit, Receive, and External/Status interrupts in both channels) has three bits associated with the interrupt source: Interrupt Pending (IP), Interrupt Under Service (IUS), and Interrupt Enable (IE). Operation of the IE bit is straightforward. If the IE bit is set for a given interrupt source, then that source can request interrupts. The exception is when the MIE (Master Interrupt Enable) bit in WR9 is reset and no interrupts may be requested. The IE bits are write only.

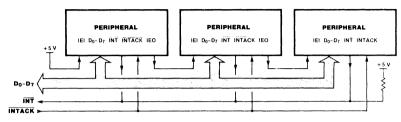

The other two bits are related to the interrupt priority chain (Figure 7). As a microprocessor peripheral, the SCC may request an interrupt only when no higher priority device is requesting one, e.g., when IEI is High. If the device in question requests an interrupt, it pulls down INT. The CPU then responds with INTACK, and the interrupting device places the vector on the data bus.

In the SCC, the IP bit signals a need for interrupt servicing. When an IP bit is 1 and the IEI input is High, the INT output is pulled Low, requesting an interrupt. In the SCC, if the IE bit is not set by enabling interrupts, then the IP for that source can never be set. The IP bits are readable in RR3A.

Figure 7. Interrupt Schedule

The IUS bits signal that an interrupt request is being serviced. If an IUS is set, all interrupt sources of lower priority in the SCC and external to the SCC are prevented from requesting interrupts. The internal interrupt sources are inhibited by the state of the internal daisy chain, while lower priority devices are inhibited by the IEO output of the SCC being pulled Low and propagated to subsequent peripherals. An IUS bit is set during an Interrupt Acknowledge cycle if there are no higher priority devices requesting interrupts.

There are three types of interrupts: Transmit, Receive, and External/Status. Each interrupt type is enabled under program control with Channel A having higher priority than Channel B, and with Receiver, Transmit, and External/Status interrupts prioritized in that order within each channel. When the Transmit interrupt is enabled, the CPU is interrupted when the transmit buffer becomes empty. (This implies that the transmitter must have had a data character written into it so that it can become empty.) When enabled, the receiver can interrupt the CPU in one of three ways:

- Interrupt on First Receive Character or Special Receive Condition.

- Interrupt on All Receive Characters or Special Receive Condition.

- Interrupt on Special Receive Condition Only.

Interrupt on First Character or Special Condition and Interrupt on Special Condition Only are typically used with the Block Transfer mode. A Special Receive Condition is one of the following: receiver overrun, framing error in Asynchronous mode, end-of-frame in SDLC mode and, optionally, a parity error. The Special Receive Condition interrupt is different from an ordinary receive character available interrupt only in the status placed in the vector during the Interrupt Acknowledge cycle. In Interrupt on First Receive Character, an interrupt can occur from Special Receive Conditions any time after the first receive character interrupt.

The main function of the External/Status interrupt is to monitor the signal transitions of the CTS, DCD, and SYNC pins; however, an External/Status interrupt is also caused by a Transmit Underrun condition, or a zero count in the baud rate generator, or by the detection of a Break (Asynchronous mode), Abort (SDLC mode) or EOP (SDLC Loop mode) sequence in the data stream. The interrupt caused by the Abort or EOP has a special feature allowing the SCC to interrupt when the Abort or EOP sequence is detected or terminated. This feature facilitates the proper termination of the current message, correct initialization of the next message, and the accurate timing of the Abort condition in external logic in SDLC mode. In SDLC Loop mode, this feature allows secondary stations to recognize the wishes of the primary station to regain control of the loop during a poll sequence.

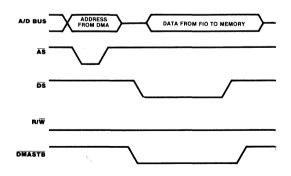

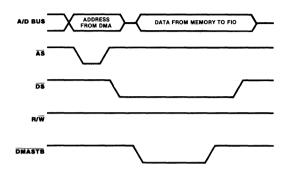

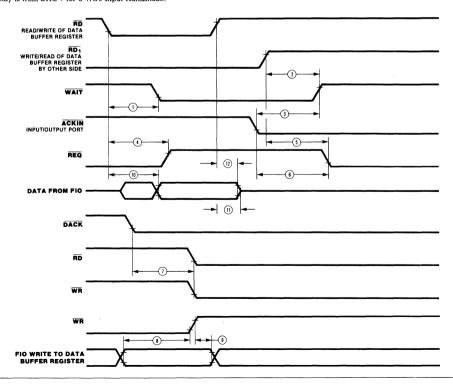

**CPU/DMA Block Transfer.** The SCC provides a Block Transfer mode to accommodate CPU block transfer functions and DMA controllers.

The Block Transfer mode uses the WAIT/ REQUEST output in conjunction with the Wait/Request bits in WR1. The WAIT/ REQUEST output can be defined under software control as a WAIT line in the CPU Block Transfer mode or as a REQUEST line in the DMA Block Transfer mode. To a DMA controller, the SCC REQUEST output indicates that the SCC is ready to transfer data to or from memory. To the CPU, the WAIT line indicates that the SCC is not ready to transfer data, thereby requesting that the CPU extend the I/O cycle. The DTR/ REQUEST line allows full-duplex operation under DMA control.

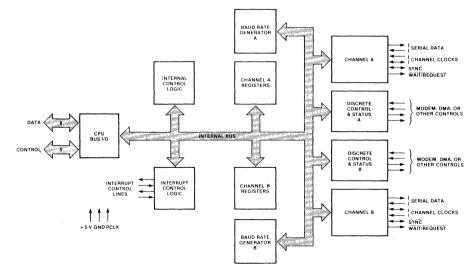

#### Architecture

The SCC internal structure includes two fullduplex channels, two baud rate generators, internal control and interrupt logic, and a bus interface to a nonmultiplexed bus. Associated with each channel are a number of read and write registers for mode control and status information, as well as logic necessary to interface to modems or other external devices (Figure 8).

The logic for both channels provides formats, synchronization, and validation for data transferred to and from the channel interface. The modem control inputs are monitored by the control logic under program control. All of the modem control signals are generalpurpose in nature and can optionally be used for functions other than modem control.

The register set for each channel includes ten control (write) registers, two synccharacter (write) registers, and four status (read) registers. In addition, each baud rate generator has two (read/write) registers for holding the time constant that determines the baud rate. Finally, associated with the interrupt logic is a write register for the interrupt vector accessible through either channel, a

Figure 8. Block Diagram of SCC Architecture

#### Architecture (Continued)

write only Master Interrupt Control register and three read registers: one containing the vector with status infomation (Channel B only), one containing the vector without status (Channel A only), and one containing the Interrupt Pending bits (Channel A only).

The registers for each channel are designated as follows:

WR0-WR15 — Write Registers 0 through 15.

RR0-RR3, RR10, RR12, RR13, RR15 — Read Registers 0 through 3, 10, 12, 13, 15.

Table 1 lists the functions assigned to each read or write register. The SCC contains only one WR2 and WR9, but they can be accessed by either channel. All other registers are paired (one for each channel).

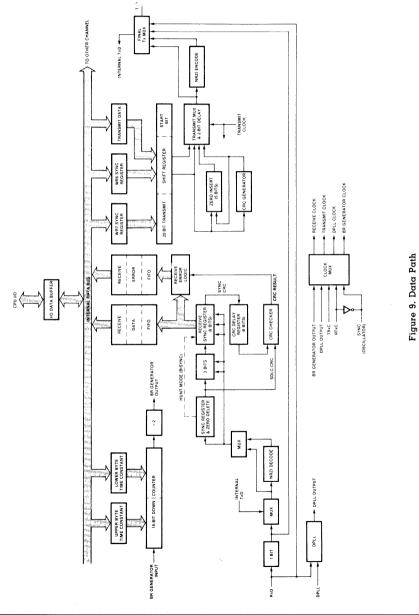

**Data Path.** The transmit and receive data path illustrated in Figure 9 is identical for both channels. The receiver has three 8-bit buffer registers in an FIFO arrangement, in addition to the 8-bit receive shift register. This scheme creates additional time for the CPU to service an interrupt at the beginning of a block of high speed data. Incoming data is routed through one of several paths (data or CRC) depending on the selected mode (the character length in Asynchronous modes also determines the data path).

The transmitter has an 8-bit Transmit Data buffer register loaded from the internal data bus and a 20-bit Transmit Shift register that can be loaded either from the synchronous character registers or from the Transmit Data register. Depending on the operational mode, outgoing data is routed through one of four main paths before it is transmitted from the Transmit Data output (TxD)

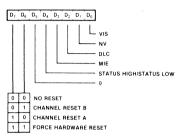

#### Programming

The SCC contains 13 write registers in each channel that are programmed by the system separately to configure the functional personality of the channels.

In the SCC, register addressing is direct for the data registers only, which are selected by a High on the  $D/\overline{C}$  pin. In all other cases (with

#### **Read Register Functions**

| RRO  | Transmit/Receive buffer status and External status                                         |

|------|--------------------------------------------------------------------------------------------|

| RR1  | Special Receive Condition status                                                           |

| RR2  | Modified interrupt vector (Channel B only)<br>Unmodified interrupt vector (Channel A only) |

| RR3  | Interrupt Pending bits (Channel A only)                                                    |

| RR8  | Receive buffer                                                                             |

| RR10 | Miscellaneous status                                                                       |

| RR12 | Lower byte of baud rate generator time constant                                            |

| RR13 | Upper byte of baud rate generator time constant                                            |

| RR15 | External/Status interrupt information                                                      |

#### Write Register Functions

| WR0  | CRC initialize, initialization commands for the various modes, Register Pointers |

|------|----------------------------------------------------------------------------------|

| WRl  | Transmit/Receive interrupt and data transfer mode definition                     |

| WR2  | Interrupt vector (accessed through either channel)                               |

| WR3  | Receive parameters and control                                                   |

| WR4  | Transmit/Receive miscellaneous parameters and modes                              |

| WR5  | Transmit parameters and controls                                                 |

| WR6  | Sync characters or SDLC address field                                            |

| WR7  | Sync character or SDLC flag                                                      |

| WR8  | Transmit buffer                                                                  |

| WR9  | Master interrupt control and reset (accessed through either channel)             |

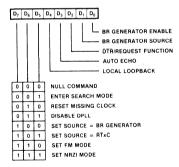

| WR10 | Miscellaneous transmitter/receiver control bits                                  |

| WR11 | Clock mode control                                                               |

| WR12 | Lower byte of baud rate generator time constant                                  |

| WR13 | Upper byte of baud rate generator time constant                                  |

| WR14 | Miscellaneous control bits                                                       |

| WR15 | External/Status interrupt control                                                |

Table 1. Read and Write Register Functions

the exception of WR0 and RR0), programming the write registers requires two write operations and reading the read registers requires both a write and a read operation. The first write is to WR0 and contains three bits that point to the selected register. The second write is the actual control word for the selected

28530 SCC

#### Programming (Continued)

register, and if the second operation is read, the selected read register is accessed. All of the registers in the SCC, including the data registers, may be accessed in this fashion. The pointer bits are automatically cleared after the read or write operation so that WR0 (or RR0) is addressed again.

The system program first issues a series of commands to initialize the basic mode of operation. This is followed by other commands to qualify conditions within the selected mode. For example, the Asynchronous mode, character length, clock rate, number of stop bits, even or odd parity might be set first. Then the interrupt mode would be set, and finally, receiver or transmitter enable.

#### Read Register 0

Dr

Ds

Ds

Ds

Ds

Ds

Ds

Image: Constraint of the state of the state

#### Read Register 1

#### **Read Register 2**

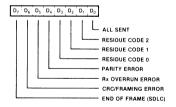

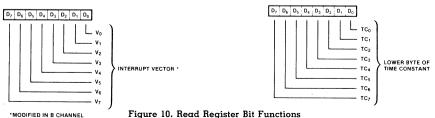

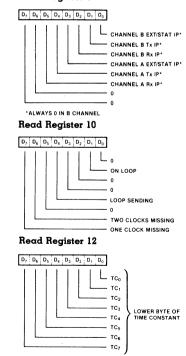

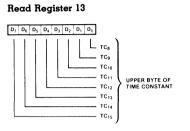

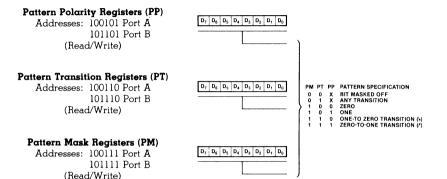

**Read Registers.** The SCC contains eight read registers (actually nine, counting the receive buffer (RR8) in each channel). Four of these may be read to obtain status information (RR0, RR1, RR10, and RR15). Two registers (RR12 and RR13) may be read to learn the baud rate generator time constant. RR2 contains either the unmodified interrupt vector (Channel A) or the vector modified by status information (Channel B). RR3 contains the Interrupt Pending (IP) bits (Channel A). Figure 10 shows the formats for each read register.

The status bits of RR0 and RR1 are carefully grouped to simplify status monitoring; e.g., when the interrupt vector indicates a Special Receive Condition interrupt, all the appropriate error bits can be read from a single register (RR1).

Read Register 3

#### Programming (Continued)

#### Read Register 15

Figure 10. Read Register Bit Functions (Continued)

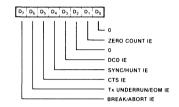

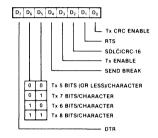

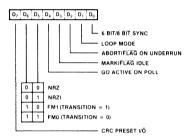

Write Register 1

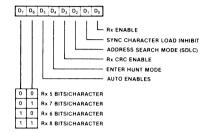

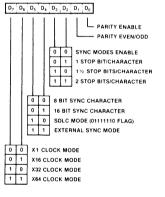

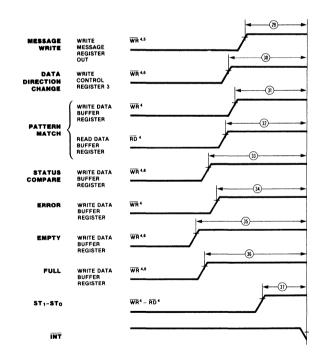

Write Registers. The SCC contains 13 write registers (14 counting WR8, the transmit buffer) in each channel. These write registers are programmed separately to configure the functional "personality" of the channels. In addition, there are two registers (WR2 and

#### WR9) shared by the two channels that may be accessed through either of them. WR2 contains the interrupt vector for both channels, while WR9 contains the interrupt control bits. Figure 11 shows the format of each write register.

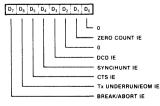

Figure 11. Write Register Bit Functions

#### Write Register 0

#### Programming (Continued)

#### Write Register 3

#### Write Register 4

#### Write Register 5

#### Write Register 6

#### Write Register 7

#### Figure 11. Write Register Bit Functions (Continued)

#### Programming (Continued)

#### Write Register 10

#### Write Register 11

#### Write Register 12

#### Write Register 13

## UPPER BYTE OF

#### Write Register 14

#### Write Register 15

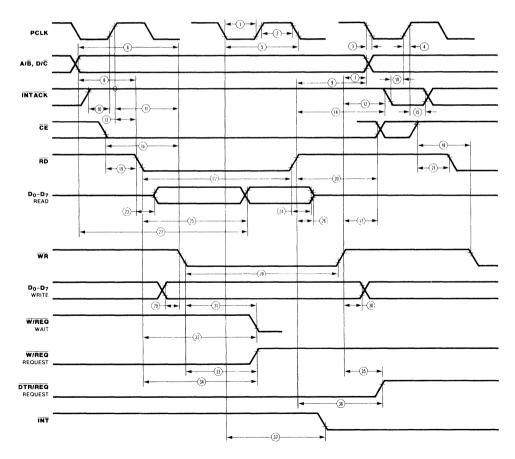

#### Timing

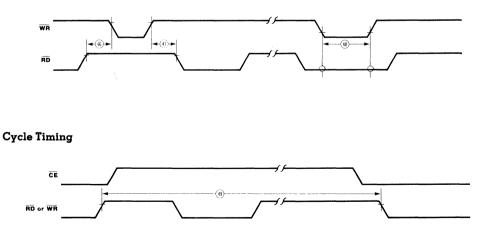

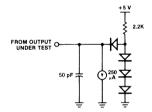

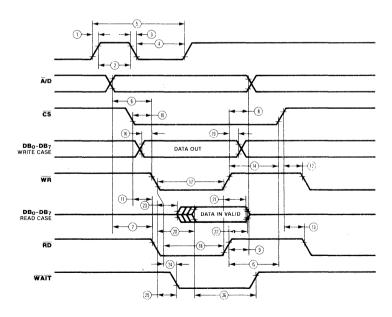

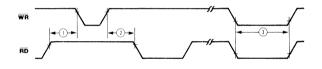

The SCC generates internal control signals from  $\overline{WR}$  and  $\overline{RD}$  that are related to PCLK. Since PCLK has no phase relationship with  $\overline{WR}$  and  $\overline{RD}$ , the circuitry generating these internal control signals must provide time for metastable conditions to disappear. This gives rise to a recovery time related to PCLK. The recovery time applies only between bus transactions involving the SCC. The recovery time required for proper operation is specified from the rising edge of  $\overline{WR}$  or  $\overline{RD}$  in the first transaction involving the SCC to the falling edge of WR or RD in the second transaction involving the SCC. This time must be at least 6 PCLK cycles plus 200 ns.

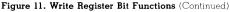

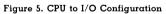

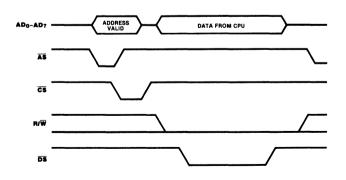

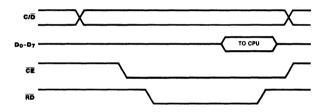

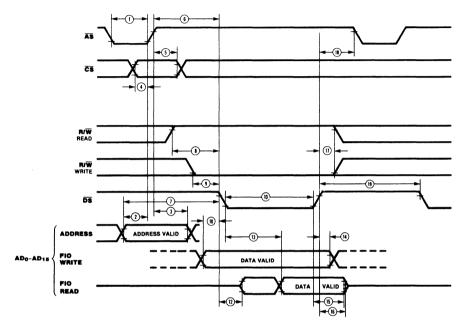

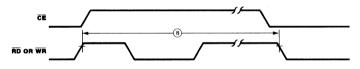

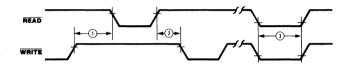

**Read Cycle Timing.** Figure 12 illustrates Read cycle timing. Addresses on A/B and D/ $\overline{C}$ and the status on INTACK must remain stable throughout the cycle. If  $\overline{CE}$  falls after  $\overline{RD}$  falls or if it rises before  $\overline{RD}$  rises, the effective  $\overline{RD}$  is shortened.

Figure 12. Read Cycle Timing

#### Timing (Continued)

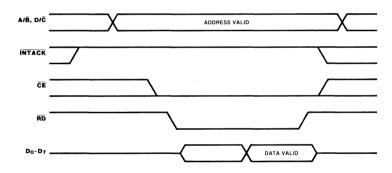

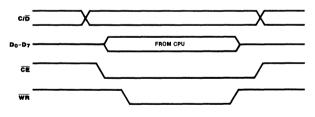

Write Cycle Timing. Figure 13 illustrates Write cycle timing. Addresses on  $A/\overline{B}$  and  $D/\overline{C}$  and the status on INTACK must remain stable

throughout the cycle. If  $\overline{CE}$  falls after  $\overline{WR}$  falls or if it rises before  $\overline{WR}$  rises, the effective  $\overline{WR}$  is shortened.

Figure 13. Write Cycle Timing

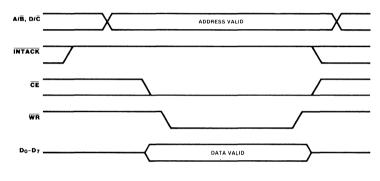

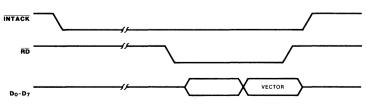

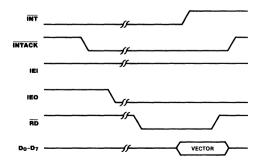

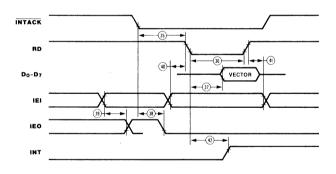

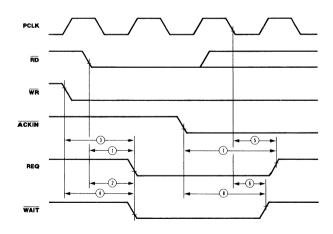

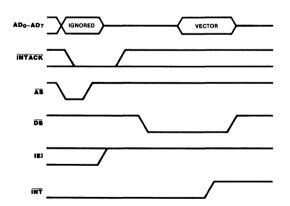

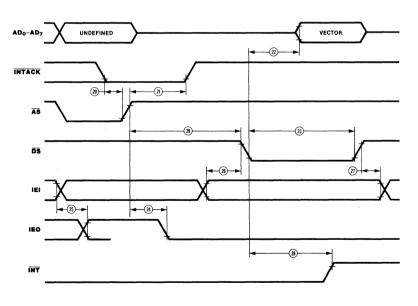

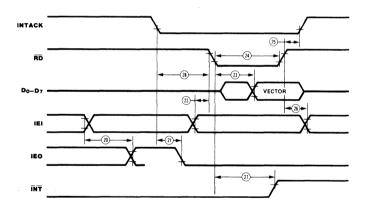

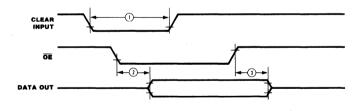

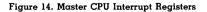

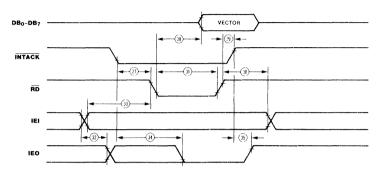

**Interrupt Acknowledge Cycle Timing.** Figure 14 illustrates Interrupt Acknowledge cycle timing. Between the time INTACK goes Low and the falling edge of RD, the internal and external IEI/IEO daisy chains settle. If there is an interrupt pending in the SCC and IEI is

High when  $\overline{RD}$  falls, the Acknowledge cycle is intended for the SCC. In this case, the SCC may be programmed to respond to  $\overline{RD}$  Low by placing its interrupt vector on D<sub>0</sub>-D<sub>7</sub> and it then sets the appropriate Interrupt-Under-Service latch internally.

Figure 14. Interrupt Acknowledge Cycle Timing

#### **Absolute Maximum Ratings**

| Voltages on all inputs and outputs   |

|--------------------------------------|

| with respect to GND0.3 V to $+7.0$ V |

| Operating Ambient                    |

| Temperature As Specified in          |

| Ordering Information                 |

| Storage Temperature65°C to +150°C    |

**Standard Test Conditions**

**DC Characteristics**

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin. Standard conditions are as follows: Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- $\blacksquare$  +4.75 V  $\leq$  V\_{\rm CC}  $\leq$  +5.25 V

- $\blacksquare$  GND = 0 V

- T<sub>A</sub> as specified in Ordering Information

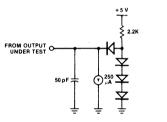

All ac parameters assume a load capacitance of 50 pF max.

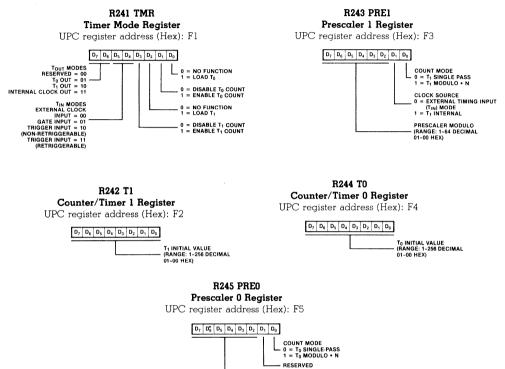

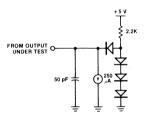

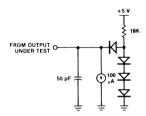

Figure 16. Open-Drain Test Load

|                           | + 5 V      |

|---------------------------|------------|

| FROM OUTPUT<br>UNDER TEST | -+K-}<br>₹ |

| 100 pF 🕇                  |            |

| Ţ                         | ŢŢ         |

Figure 15. Standard Test Load

| Symbol          | Parameter                      | Min  | Max                  | Unit | Condition                    |

|-----------------|--------------------------------|------|----------------------|------|------------------------------|

| V <sub>IH</sub> | Input High Voltage             | 2.0  | V <sub>CC</sub> +0.3 | V    |                              |

| V <sub>IL</sub> | Input Low Voltage              | -0.3 | 0.8                  | V    |                              |

| V <sub>OH</sub> | Output High Voltage            | 2.4  |                      | V    | $I_{OH} = -250 \ \mu A$      |

| V <sub>OL</sub> | Output Low Voltage             |      | 0.4                  | V    | $I_{OL} = +2.0 \text{ mA}$   |

| IIL             | Input Leakage                  |      | ±10.0                | μA   | $0.4 \leq V_{IN} \leq +2.4V$ |

| I <sub>OL</sub> | Output Leakage                 |      | ±10.0                | μA   | $0.4 \le V_{OUT} \le +2.4V$  |

| I <sub>CC</sub> | V <sub>CC</sub> Supply Current |      | 250                  | mA   |                              |

$V_{CC}$  = 5 V ± 5% unless otherwise specified, over specified temperature range.

#### Capacitance

| Symbol                                                                        | Parameter                         | Min  | Μαχ | Unit | Test Condition       |

|-------------------------------------------------------------------------------|-----------------------------------|------|-----|------|----------------------|

| C <sub>IN</sub>                                                               | C <sub>IN</sub> Input Capacitance |      | 10  | pF   | Unmeasured Pins      |

| C <sub>OUT</sub> Output Capacitance<br>C <sub>I/O</sub> Bidirectional Capacit |                                   |      | 15  | pF   | Returned to Ground   |

|                                                                               |                                   | ance | 20  | pF   | notarinoa to circana |

f = 1 MHz, over specified temperature range.

#### **Read and Write Timing**

| Number | Symbol           | Parameters                                      | Min(ns) | Max(ns) | Notes* |

|--------|------------------|-------------------------------------------------|---------|---------|--------|

| 1      | TwPC1            | PCLK Low Width                                  | 105     | 2000    |        |

| 2      | TwPCh            | PCLK High Width                                 | 105     | 2000    |        |

| 3      | TfPC             | PCLK Fall Time                                  |         | 20      |        |

| 4      | TrPC             | PCLK Rise Time                                  |         | 20      |        |

| 5      | TcPC             | PCLK Cycle Time                                 | 250     | 4000    |        |

| 6      | TsA(WR)          | Address to WR   Setup Time                      | 80      |         |        |

| 7      | Th <b>A</b> (WR) | Address to WR † Hold Time                       | 0       |         |        |

| 8      | TsA(RD)          | Address to RD ↓ Setup Time                      | 80      |         |        |

| 9      | ThA(RD)          | Address to $\overline{\mathrm{RD}}$ † Hold Time | 0       |         |        |

| 10     | TsIA(PC)         | INTACK to PCLK 1 Setup Time                     | 0       |         |        |

| 11     | TsIAi(WR)        | INTACK to WR   Setup Time                       | 200     |         | 1      |

| 12     | ThIA(WR)         | INTACK to WR   Hold Time                        | 0       |         |        |

| 13     | TsIAi(RD)        | INTACK to RD   Setup Time                       | 200     |         | 1      |

| 14     | ThIA(RD)         | INTACK to RD † Hold Time                        | 0       |         |        |

| 15     | ThIA(PC)         | INTACK to PCLK   Hold Time                      | 100     |         |        |

| 16     | TsCE1(WR)        | CE Low to WR ↓ Setup Time                       | 0       |         |        |

| 17     | ThCE(WR)         | CE to WR † Hold Time                            | 0       |         |        |

| 18     | TsCEh(WR)        | CE High to WR↓ Setup Time                       | 100     |         |        |

| 19     | TsCE1(RD)        | CE Low to RD ↓ Setup Time                       | 0       |         | 1      |

| 20     | ThCE(RD)         | CE to RD † Hold Time                            | 0       |         | 1      |

| 21     | TsCEh(RD)        | CE High to RD   Setup Time                      | 100     |         | 1      |

| 22     | TwRD1            | RD Low Width                                    | 390     |         | 1      |

| 23     | TdRD(DRA)        | RD ↓ to Read Data Active Delay                  | 0       |         |        |

| 24     | TdRDr(DR)        | RD † to Read Data Not Valid Delay               | 0       |         |        |

| 25     | TdRDf(DR)        | RD ↓ to Read Data Valid Delay                   |         | 255     |        |

| 26     | TdRD(DRz)        | RD † to Read Data Float Delay                   |         | 70      | 2      |

#### Read and Write Timing (Continued)

NOTES:

1. Parameter does not apply to Interrupt Acknowledge transactions.

2. Float delay is defined as the time required for a  $\pm 0.5$  V change in the output with a maximum dc load and minimum ac load.

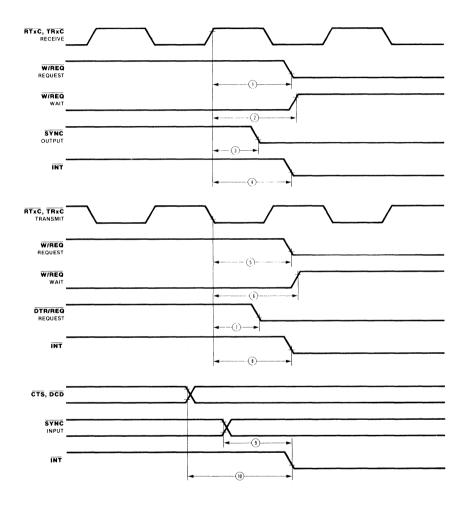

#### Interrupt Acknowledge Timing

#### **Reset Timing**

| Number | Symbol          | Parameters                                             | Min(ns) | Max(ns) | Notes* |

|--------|-----------------|--------------------------------------------------------|---------|---------|--------|

| 27     | TdA(DR)         | Address Required Valid to Read Data Valid Delay        |         | 590     |        |

| 28     | TwWR1           | WR Low Width                                           | 390     |         |        |

| 29     | TsDW(WR)        | Write Data to WR I Setup Time                          | 0       |         |        |

| 30     | ThDW(WR)        | Write Data to WR 1 Hold Time                           | 0       |         |        |

| 31     | - TdWR(W)       | WR↓ to Wait Valid Delay                                |         |         |        |

| 32     | TdRD(W)         | RD↓ to Wait Valid Delay                                |         | 240     | 4      |

| 33     | TdWRf(REQ)      | WR I to W/REQ Not Valid Delay                          |         | 240     |        |

| 34     | TdRDf(REQ)      | RD 1 to W/REQ Not Valid Delay                          |         | 240     |        |

| 35     | TdWRr(REQ)      | WR 1 to DTR/REQ Not Valid Delay                        |         | 5TcPC   |        |

|        |                 |                                                        |         | + 300   |        |

| 36     | - TdRDr(REQ)    |                                                        |         | -5TcPC  |        |

|        |                 |                                                        |         | + 300   |        |

| 37     | TdPC(INT)       | PCLK 4 to INT Valid Delay                              |         | 500     | 4      |

| 38     | TdIAi(RD)       | INTACK to RD ↓ (Acknowledge) Delay                     |         |         | 5      |

| 39     | TwRDA           | RD (Acknowledge) Width                                 | 285     |         |        |

| 40     | – TdRDA(DR) ––– | — RD ↓ (Acknowledge) to Read Data Valid Delay ——       |         | 190     |        |

| 41     | TsIEI(RDA)      | IEI to RD ↓ (Acknowledge) Setup Time                   | 120     |         |        |

| 42     | ThIEI(RDA)      | IEI to $\overline{	ext{RD}}$ † (Acknowledge) Hold Time | 0       |         |        |

| 43     | TdIEI(IEO)      | IEI to IEO Delay Time                                  |         | 120     |        |

| 44     | TdPC(IEO)       | PCLK † to IEO Delay                                    |         | 250     |        |

| 45     | – TdRDA(INT) —  | - RD I to INT Inactive Delay                           |         | 500     |        |

| 46     | TdRD(WRQ)       | RD 1 to WR I Delay for No Reset                        | 30      |         |        |

| 47     | TdWRQ(RD)       | WR ↑ to RD ↓ Delay for No Reset                        | 30      |         |        |

| 48     | TwRES           | WR and RD Coincident Low for Reset                     | 250     |         |        |

| 49     | Trc             | Valid Access Recovery Time                             | 6TcPC   |         |        |

|        |                 |                                                        | + 200   |         | 3      |

NOTES:

3. Parameter applies only between transactions involving the SCC.

Open-drain output, measured with open-drain test load.

Parameter is system dependent. For any SCC in the daisy chain, TdIAi(RD) must be greater than the sum of TdPC(IEO)

for the highest priority device in the daisy chain, TsIEI(RDA) for the SCC, and TdIEIf(IEO) for each device separating them in the daisy chain.

\*Timings are preliminary and subject to change.

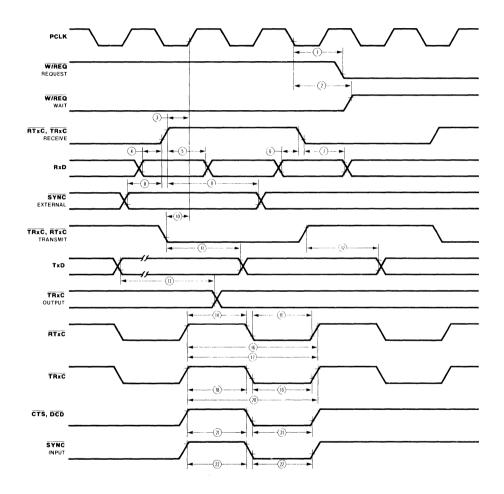

#### General Timing

| Number | Symbol         | Parameters                                                                 | Min(ns)        | Max(ns) | Notes* |

|--------|----------------|----------------------------------------------------------------------------|----------------|---------|--------|

| 1      | TdPC(REQ)      | PCLK I to W/REQ Valid Delay                                                |                | 250     |        |

| 2      | TdPC(W)        | PCLK↓ to Wait Inactive Delay                                               |                | 350     |        |

| 3      | TsRXC(PC)      | RxC † to PCLK † Setup Time                                                 | 50             |         | 1,4    |

| 4      | TsRXD(RXCr)    | $RxD$ to $\overline{RxC}$ † Setup Time (X1 Mode)                           | 0              |         | 1      |

| 5      | — ThRXD(RXCr)- | -RxD to RxC † Hold Time (X1 Mode)                                          |                |         | l      |

| 6      | TsRXD(RXCf)    | RxD to $\overline{RxC}$ + Setup Time (X1 Mode)                             | 0              |         | 1,5    |

| 7      | ThRXD(RXCf)    | RxD to $\overline{RxC} \downarrow$ Hold Time (X1 Mode)                     | 150            |         | 1,5    |

| 8      | TsSY(RXC)      | SYNC to RxC 1 Setup Time                                                   | -200           |         | 1      |

| 9      | ThSY(RXC)      | $\overline{\text{SYNC}}$ to $\overline{\text{RXC}}$ <sup>†</sup> Hold Time | 3TcPC<br>+ 200 |         | 1      |

| 10     | — TsTXC(PC) —— |                                                                            | 0              |         |        |

| 11     | TdTXCf(TXD)    | TxC↓ to TxD Delay (X1 Mode)                                                |                | 300     | 2      |

| 12     | TdTXCr(TXD)    | $\overline{\text{TxC}}$ † to TxD Delay (X1 Mode)                           |                | 300     | 2,5    |

| 13     | TdTXD(TRX)     | TxD to TRxC Delay (Send Clock Echo)                                        |                |         |        |

| 14     | TwRTXh         | RTxC High Width                                                            | 180            |         |        |

| 15     | TwRTX1         | - RTxC Low Width                                                           | 180            |         |        |

| 16     | TcRTX          | RTxC Cycle Time                                                            | 400            |         |        |

| 17     | TcRTXX         | Crystal Oscillator Period                                                  | 250            | 1000    | 3      |

| 18     | TwTRXh         | TRxC High Width                                                            | 180            |         |        |

| 19     | TwTRX1         | TRxC Low Width                                                             | 180            |         |        |

| 20     | — TcTRX ———    | - TRxC Cycle Time                                                          | 400            |         |        |

| 21     | TwEXT          | DCD or CTS Pulse Width                                                     | 200            |         |        |

| 22     | TwSY           | SYNC Pulse Width                                                           | 200            |         |        |

NOTES: 1.  $\overline{RxC}$  is  $\overline{RTxC}$  or  $\overline{TRxC}$ , whichever is supplying the receive

$\begin{array}{l} \text{Intro is Intro or TRXC, which even is supplying the transmit}\\ \text{Clock.}\\ \text{3. TrXC is TRXC or RTXC, which even is supplying the transmit}\\ \text{Clock.}\\ \text{3. Both RTXC and SYNC have 30 pF capacitors to ground con-$

nected to them.

Parameter applies only if the data rate is one-fourth the PCLK rate. In all other cases, no phase relationship between RxC and PCLK or TxC and PCLK is required.

5. Parameter applies only to FM encoding/decoding.

\*Timings are preliminary and subject to change.

#### General Timing (Continued)

#### System Timing

| Number | Symbol         | Parameter                                                                                            | Min | Μαχ | Units  | Notes* |

|--------|----------------|------------------------------------------------------------------------------------------------------|-----|-----|--------|--------|

| 1      | TdRXC (REQ)    | RxC † to W/REQ Valid Delay                                                                           | 8   | 12  | TcPC   | 2      |

| 2      | TdRXC(W)       | RxC † to Wait Inactive Delay                                                                         | 8   | 12  | TcPC   | 1,2    |

| 3      | TdRXC(SY)      | RxC † to SYNC Valid Delay                                                                            | 4   | 7   | TcPC   | 2      |

| 4      | TdRXC(INT)     | RxC 1 to INT Valid Delay                                                                             | 10  | 16  | TcPC   | 1,2    |

| 5      | — TdTXC(REQ) — | - TxC I to W/REQ Valid Delay-                                                                        | 5   | 8   | TcPC - | 3      |

| 6      | TdTXC(W)       | TxC ↓ to Wait Inactive Delay                                                                         | 5   | 8   | TcPC   | 1,3    |

| 7      | TdTXC(DRQ)     | TxC I to DTR/REQ Valid Delay                                                                         | 4   | 7   | TcPC   | 3      |

| 8      | TdTXC(INT)     | TxC I to INT Valid Delay                                                                             | 6   | 10  | TcPC   | 1,3    |

| 9      | TdSY(INT)      | SYNC Transition to INT Valid Delay                                                                   | 2   | 6   | TcPC   | 1      |

| 10     | TdEXT(INT)     | $\overline{\text{DCD}}$ or $\overline{\text{CTS}}$ Transition to $\overline{\text{INT}}$ Valid Delay | 2   | 6   | TcPC   | 1      |

#### System Timing (Continued)

NOTES:

3.  $\overline{TxC}$  is  $\overline{TRxC}$  or  $\overline{RTxC}$ , whichever is supplying the transmit clock. \*Timings are preliminary and subject to change.

Z8530 SCC

Open-drain output, measured with open-drain test load.

RxC is RTxC or TRxC, whichever is supplying the receive clock.

#### Ordering Information

| Туре                        | Package                                                              | Temp                                         | Clock | Description                               |

|-----------------------------|----------------------------------------------------------------------|----------------------------------------------|-------|-------------------------------------------|

| Z8530 B1<br>B6<br>D1        | Plastic 40 pin<br>Plastic 40 pin<br>Ceramic 40 pin                   | 0/+70°C<br>-40/+85°C<br>0/+70°C              | 4MHz  | Z8530 Serial Communications<br>Controller |

| D2<br>D6                    | Ceramic 40 pin<br>Ceramic 40 pin                                     | -5S/+125°C<br>-40/+85°C                      |       |                                           |

| Z8530A B1<br>B6<br>D1<br>D6 | Plastic 40 pin<br>Plastic 40 pin<br>Ceramic 40 pin<br>Ceramic 40 pin | 0/+70°C<br>-40/+85°C<br>0/+70°C<br>-40/+85°C | 6MHz  |                                           |

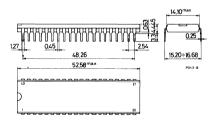

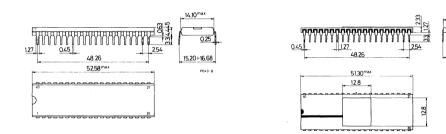

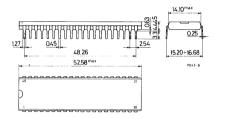

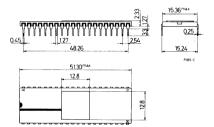

#### Packages

Plastic

Ceramic

### Counter/Timer and Parallel I/O Unit

#### Features

- Two independent 8-bit, double-buffered, bidirectional I/O ports plus a 4-bit special-purpose I/O port. I/O ports feature programmable polarity, programmable direction (Bit mode), "pulse catchers," and programmable opendrain outputs.

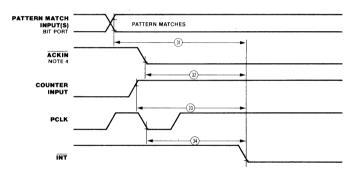

- Four handshake modes, including 3-Wire (like the IEEE-488).

- REQUEST/WAIT signal for high-speed data transfer.

#### **General Description**

The Z8536 CIO Counter/Timer and Parallel I/O element is a general-purpose peripheral circuit, satisfying most counter/ timer and parallel I/O needs encountered in system designs. This versatile device contains three I/O ports and three counter/timers. Many programmable options tailor its configuration to specific applications. The use of the device is simplified by making all internal registers

- Flexible pattern-recognition logic, programmable as a 16-vector interrupt controller.

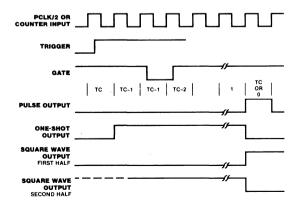

- Three independent 16-bit counter/timers with up to four external access lines per counter/timer (count input, output, gate, and trigger), and three output duty cycles (pulsed, one-shot, and square-wave), programmable as retriggerable or nonretriggerable.

- Easy to use since all registers are read/write.

(command, status, and data) readable and (except for status bits) writable. In addition, each register is given its own unique internal address, so that any register can be accessed in two operations. All data registers can be directly accessed in a single operation. The CIO is easily interfaced to all popular microprocessors.

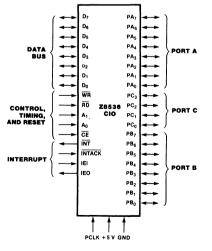

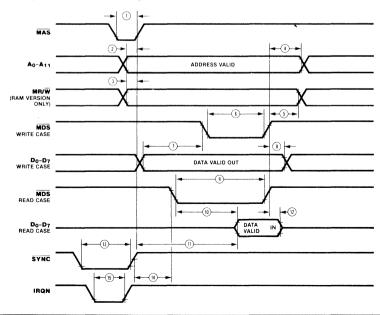

Figure 1. Logic Functions

Figure 2. Pin Configurations

### **Pin Description**

**A<sub>0</sub>-A<sub>1</sub>.** Address Lines (input). These two lines are used to select the register involved in the CPU transaction: Port A's Data register, Port B's Data register, Port C's Data register, or a control register.

**CE.** Chip Enable (input, active Low). A Low level on this input enables the CIO to be read from or written to.

**D**<sub>0</sub>-**D**<sub>7</sub>. Data Bus (bidirectional 3-state). These eight data lines are used for transfers between the CPU and the CIO.

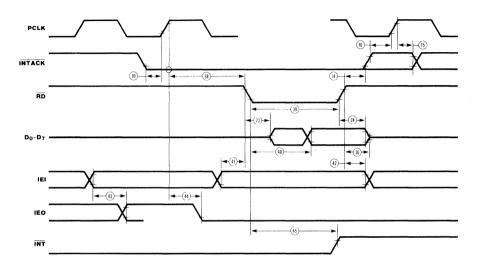

**IEI.** Interrupt Enable In (input, active High). IEI is used with IEO to form an interrupt daisy chain when there is more than one interruptdriven device. A High IEI indicates that no other higher priority device has an interrupt under service or is requesting an interrupt.

**IEO.** Interrupt Enable Out (output, active High). IEO is High only if IEI is High and the CPU is not servicing an interrupt from the requesting CIO or is not requesting an interrupt (Interrupt Acknowledge cycle only). IEO is connected to the next lower priority device's IEI input and thus inhibits interrupts from lower priority devices.

**INT.** Interrupt Request (output, open-drain, active Low). This signal is pulled Low when the CIO requests an interrupt.

**INTACK.** Interrupt Acknowledge (input, active Low). This input indicates to the CIO that an <u>Interrupt</u> Acknowledge cycle is in progress. <u>INTACK</u> must be synchronized to PCLK, and it must be stable throughout the Interrupt Acknowledge cycle.

**PA<sub>0</sub>-PA<sub>7</sub>.** Port A I/O lines (bidirectional, 3-state, or open-drain). These eight I/O lines transfer information between the CIO's Port A and external devices.

**PB<sub>0</sub>-PB<sub>7</sub>.** Port B I/O lines (bidirectional, 3-state, or open-drain). These eight I/O lines transfer information between the CIO's Port B and external devices. May also be used to provide external access to Counter/Timers 1 and 2.

**PC<sub>0</sub>-PC<sub>3</sub>.** Port C I/O lines (bidirectional, 3-state, or open-drain). These four I/O lines are used to provide handshake, WAIT, and REQUEST lines for Ports A and B or to provide external access to Counter/Timer 3 or access to the CIO's Port C.

**PCLK.** Peripheral Clock (input, TTLcompatible). This is the clock used by the internal control logic and the counter/timers in timer mode. It does not have to be the CPU clock.

**RD\*.** Read (input, active Low). This signal indicates that a CPU is reading from the CIO. During an Interrupt Acknowledge cycle, this signal gates the interrupt vector onto the data bus if the CIO is the highest priority device requesting an interrupt.

**WR\*.** Write (input, active Low). This signal indicates a CPU write to the CIO.

\*When  $\overline{RD}$  and  $\overline{WR}$  are detected Low at the same time (normally an illegal condition), the CIO is reset.

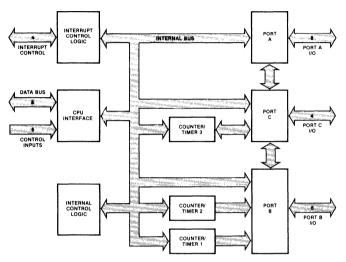

### Architecture

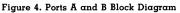

The CIO Counter/Timer and Parallel I/O element (Figure 3) consists of a CPU interface, three I/O ports (two general-purpose 8-bit ports and one special-purpose 4-bit port), three 16-bit counter/timers, an interruptcontrol logic block, and the internal-control logic block. An extensive number of programmable options allow the user to tailor the configuration to best suit the specific application.

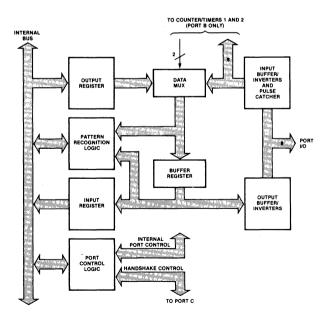

The two general-purpose 8-bit I/O ports

(Figure 4) are identical, except that Port B can be specified to provide external access to Counter/Timers 1 and 2. Either port can be programmed to be a handshake-driven, double-buffered port (input, output, or bidirectional) or a control-type port with the direction of each bit individually programmable. Each port includes pattern-recognition logic, allowing interrupt generation when a specific pattern is detected. The pattern-recognition logic

### Architecture (Continued)

Figure 3. CIO Block Diagram

### Architecture (Continued)

can be programmed so the port functions like a priority-interrupt controller. Ports A and B can also be linked to form a 16-bit I/O port.

To control these capabilities, both ports contain 12 registers. Three of these registers, the Input, Output, and Buffer registers, comprise the data path registers. Two registers, the Mode Specification and Handshake Specification registers, are used to define the mode of the port and to specify which handshake, if any, is to be used. The reference pattern for the pattern-recognition logic is defined via three registers: the Pattern Polarity, Pattern Transition, and Pattern Mask registers. The detailed characteristics of each bit path (for example, the direction of data flow or whether a path is inverting or noninverting) are programmed using the Data Path Polarity, Data Direction, and Special I/O Control registers.

The primary control and status bits are

grouped in a single register, the Command and Status register, so that after the port is initially configured, only this register must be accessed frequently. To facilitate initialization, the port logic is designed so that registers associated with an unrequired capability are ignored and do not have to be programmed.

The function of the special-purpose 4-bit port, Port C (Figure 5), depends upon the roles of Ports A and B. Port C provides the required handshake lines. Any bits of Port C not used as handshake lines can be used as I/O lines or to provide external access for the third counter/timer.

Since Port C's function is defined primarily by Ports A and B, only three registers (besides the Data Input and Output registers) are needed. These registers specify the details of each bit path: the Data Path Polarity, Data Direction, and Special I/O Control registers.

Figure 5. Port C Block Diagram

Architecture (Continued)

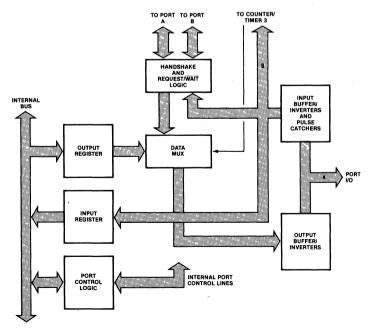

The three counter/timers (Figure 6) are all identical. Each is comprised of a 16-bit downcounter, a 16-bit Time Constant register (which holds the value loaded into the downcounter), a 16-bit Current Count register (used to read the contents of the down-counter), and two 8-bit registers for control and status (the Mode Specification and the Command and Status registers).

The capabilities of the counter/timer are numerous. Up to four port I/O lines can be dedicated as external access lines for each counter/timer: counter input, gate input, trigger input, and counter/timer output. Three different counter/timer output duty cycles are available: pulse, one-shot, or square-wave. The operation of the counter/timer can be programmed as either retriggerable or nonretriggerable. With these and other options, most counter/timer applications are covered.

78536 CIO

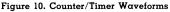

There are five registers (Master Interrupt Control register, three Interrupt Vector registers, and the Current Vector register) associated with the interrupt logic. In addition, the ports' Command and Status registers and the counter/timers' Command and Status registers include bits associated with the interrupt logic. Each of these registers contains three bits for interrupt control and status: Interrupt Pending (IP), Interrupt Under Service (IUS), and Interrupt Enable (IE).

### Figure 6. Counter/Timer Block Diagram

### **Functional Description**

The following describes the functions of the ports, pattern-recognition logic, counter/timers, and interrupt logic.

I/O Port Operations. Of the CIO's three I/O ports, two (Ports A and B) are generalpurpose, and the third (Port C) is a specialpurpose 4-bit port. Ports A and B can be configured as input, output, or bidirectional ports with handshake. (Four different handshakes are available.) They can also be linked to form a single 16-bit port. If they are not used as ports with handshake, they provide 16 input or output bits with the data direction programmable on a bit-by-bit basis. Port B also provides access for Counter/Timers 1 and 2. In all configurations. Ports A and B can be programmed to recognize specific data patterns and to generate interrupts when the pattern is encountered.

The four bits of Port C provide the handshake lines for Ports A and B when required. A REQUEST/WAIT line can also be provided so that CIO transfers can be synchronized with DMAs or CPUs. Any Port C bits not used for handshake or REQUEST/WAIT can be used as input or output bits (individually data-direction programmable) or external access lines for Counter/Timer 3. Port C does not contain any pattern-recognition logic. It is, however, capable of bit-addressable writes. With this feature, any combination of bits can be set and/or cleared while the other bits remain undisturbed without first reading the register.

Bit Port Operations. In bit port operations, the port's Data Direction register specifies the direction of data flow for each bit. A 1 specifies an input bit, and a 0 specifies an output bit. If bits are used as I/O bits for a counter/timer, they should be set as input or output, as required.

The Data Path Polarity register provides the capability of inverting the data path. A 1 specifies inverting, and a 0 specifies non-inverting. All discussions of the port operations assume that the path is noninverting.

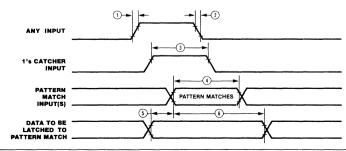

The value returned when reading an input bit reflects the state of the input just prior to the read. A l's catcher can be inserted into the input data path by programming a l to the corresponding bit position of the port's Special I/O Control register. When a l is detected at the l's catcher input, its output is set to l until it is cleared. The l's catcher is cleared by writing a 0 to the bit. In all other cases, attempted writes to input bits are ignored.

When Ports A and B include output bits, reading the Data register returns the value being output. Reads of Port C return the state of the pin. Outputs can be specified as opendrain by writing a 1 to the corresponding bit of the port's Special I/O Control register. Port C has the additional feature of bit-addressable writes. When writing to Port C, the four most significant bits are used as a write protect mask for the least significant bits (0-4, 1-5, 2-6, and 3-7). If the write protect bit is written with a 1, the state of the corresponding output bit is not changed.

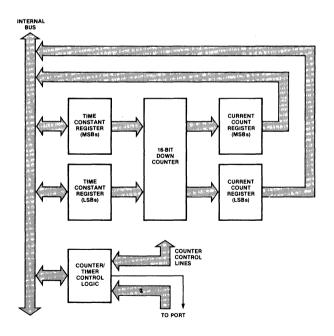

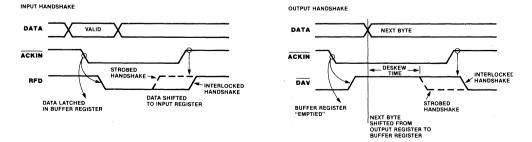

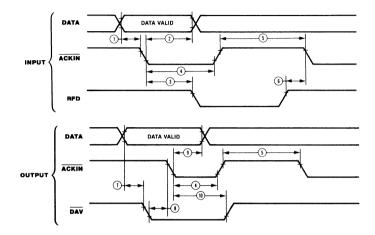

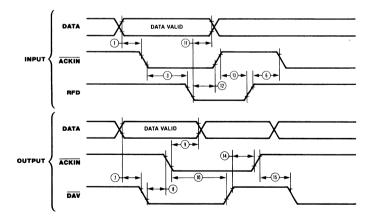

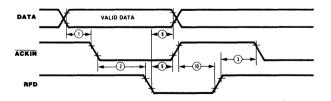

Ports with Handshake Operation. Ports A and B can be specified as 8-bit input, output, or bidirectional ports with handshake. The CIO provides four different handshakes for its ports: Interlocked, Strobed, Pulsed, and 3-Wire. When specified as a port with handshake, the transfer of data into and out of the port and interrupt generation is under control of the handshake logic. Port C provides the handshake lines as shown in Table 1. Any Port C lines not used for handshake can be used as simple I/O lines or as access lines for Counter/Timer 3.

When Ports A and B are configured as ports with handshake, they are double-buffered. This allows for more relaxed interrupt service routine response time. A second byte can be input to or output from the port before the interrupt for the first byte is serviced. Normally, the Interrupt Pending (IP) bit is set and an interrupt is generated when data is shifted into the Input register (input port) or out of the Output register (output port). For input and output ports, the IP is automatically cleared when the data is read or written. In bidirectional ports, IP is cleared only by command.

When the Interrupt on Two Bytes (ITB) control bit is set to 1, interrupts are generated only when two bytes of data are available to be read or written. This allows a minimum of 16 bits of information to be transferred on each interrupt. With ITB set, the IP is not automatically cleared until the second byte of data is read or written.

When the Single Buffer (SB) bit is set to 1, the port acts as if it is only single-buffered. This is useful if the handshake line must be stopped on a byte-by-byte basis.

Ports A and B can be linked to form a 16-bit port by programming a 1 in the Port Link Control (PLC) bit. In this mode, only Port A's Handshake Specification and Command and Status registers are used. Port B must be specified as a bit port. When linked, only Port A has pattern-match capability. Port B's pattern-match capability must be disabled. Also, when the ports are linked, Port B's Data register must be read or written before Port A's.

When a port is specified as a port with handshake, the type of port it is (input, output, or bidirectional) determines the direction of data flow. The data direction for the bidirectional port is determined by a bit in Port C (Table 1) In all cases, the contents of the Data Direction register are ignored. The contents of the Special I/O Control register apply only to output bits (3-state or open-drain). Inputs may not have I's catchers; therefore, those bits in the Special I/O Control register are ignored. Port C lines used for handshake should be programmed as inputs. The handshake specification overrides Port C's Data Direction register for bits that must be outputs. The contents of Port C's Data Path Polarity register still apply.

78536 CIO

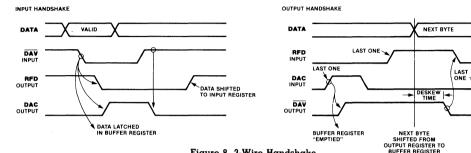

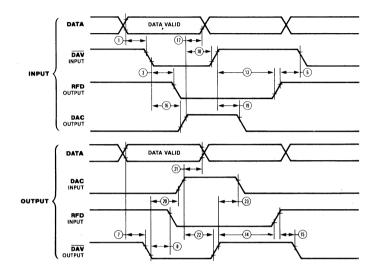

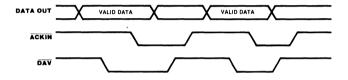

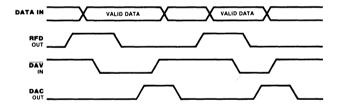

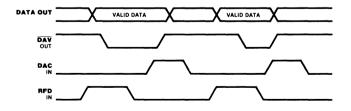

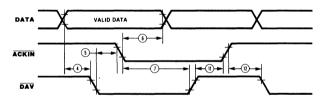

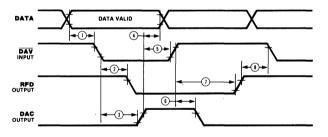

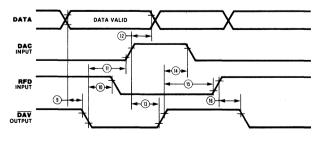

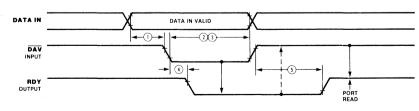

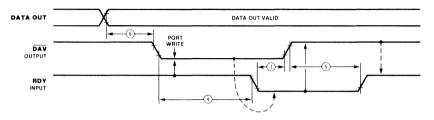

Interlocked Handshake. In the Interlocked Handshake mode, the action of the CIO must be acknowledged by the external device before the next action can take place. Figure 7 shows timing for Interlocked Handshake. An output port does not indicate that new data is available until the external device indicates it is ready for the data. Similarly, an input port does not indicate that it is ready for new data until the data source indicates that the previous byte of the data is no longer available, thereby acknowledging the input port's acceptance of the last byte. This allows the CIO to interface directly to the port of a Z8 microcomputer, a UPC, an FIO, an FIFO, or to another CIO port with no external logic.

A 4-bit deskew timer can be inserted in the Data Available ( $\overline{DAV}$ ) output for output ports. As data is transferred to the Buffer register, the deskew timer is triggered. After the number of PCLK cycles specified by the

| Port A/B Configuration                                                          | PC3                        | PC <sub>2</sub> | PC1                        | PC0          |

|---------------------------------------------------------------------------------|----------------------------|-----------------|----------------------------|--------------|

| Ports A and B: Bit Ports                                                        | Bit I/O                    | Bit I/O         | Bit I/O                    | Bit I/O      |

| Port A: Input or Output Port<br>(Interlocked, Strobed, or Pulsed<br>Handshake)* | RFD or DAV                 | ACKIN           | REQUEST/WAIT<br>or Bit I/O | Bit I/O      |

| Port B: Input or Output Port<br>(Interlocked, Strobed, or Pulsed<br>Handshake)* | REQUEST/WAIT<br>or Bit I/O | Bit I/O         | RFD or DAV                 | ACKIN        |

| Port A or B: Input Port (3-Wire<br>Handshake)                                   | RFD (Output)               | DAV (Input)     | REQUEST/WAIT<br>or Bit I/O | DAC (Output) |

| Port A or B: Output Port (3-Wire<br>Handshake)                                  | DAV (Output)               | DAC (Input)     | REQUEST/WAIT<br>or Bit I/O | RFD (Input)  |

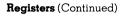

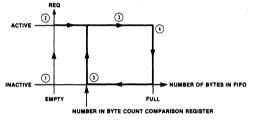

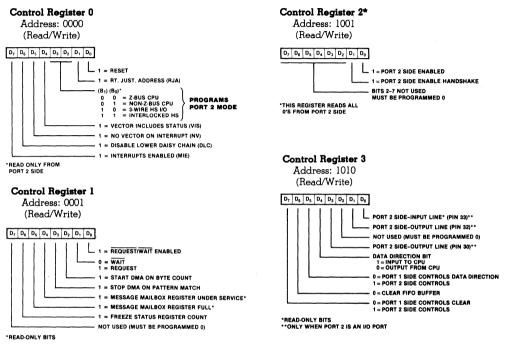

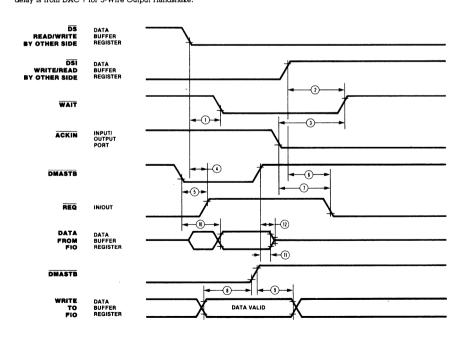

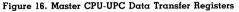

| Port A or B: Bidirectional Port<br>(Interlocked or Strobed Handshake)           | RFD or DAV                 | ACKIN           | REQUEST/WAIT<br>or Bit I/O | IN/OUT       |